## ТЕСТИРОВАНИЕ КОМБИНАЦИОННЫХ СХЕМ С НЕИСПРАВНОСТЬЮ ТИПА ЗАДЕРЖКА ПУТИ

П.Е. Селиванов (г. Томск, Томский политехнический университет) E-mail: paulishere@mail.ru

## PATH DELAY FAULT TESTING FOR COMBINATIONAL CIRCUITS

P.E. Selivanov (Tomsk, Tomsk Polytechnik University)

**Abstract.** In this paper the problems of path delay faults are analyzed. Multi-valued alphabet approach is presented. The combinational circuit was tested using multi-valued alphabet and the test vectors are analyzed.

**Keywords:** path delay faults, combinational circuits, multi-valued alphabet, 16-valued alphabet, path delay testing.

**Введение.** В практике проектирования ЭВМ накоплен огромный опыт по синтезу различных схем. Такие устройства как дешифраторы, шифраторы, схемы сравнения, комбинационные сумматоры, коммутаторы и др. являются комбинационными схемами, применение которых очень развито в современном проектировании цифровых устройств [1]. Правильное функционирование цифрового устройства возможно только в том случае, если времена распространения сигналов вдоль путей логической схемы лежат в определенных пределах. Когда время распространения сигнала выходит за эти пределы, говорят, что имеет место неисправность типа задержки сигнала. В подавляющем большинстве эти неисправности приводят к увеличению времени распространения сигналов [2].

Задержка пути. Рассмотрим исправную схему. В разные моменты времени t1, t2 на неё поступают 2 набора входных значений с определённым промежутком времени. При этом на выходе схемы появляются соответствующие значения 0, 1. Если через промежуток времени, значение схемы в момент t2 не поменяется с 0 на 1, то имеет место неисправность типа задержка путей [3].

**Многозначный алфавит.** В двоичном алфавите хорошо моделируется статическое поведение логических схем для установившихся значений сигналов, но при этом не учитываются переходные процессы, возникающие при смене значений входных сигналов, и появляется потребность рассматривать отдельно исправную и неисправную схемы. В силу этого получили распространение алфавиты большей значности. В основе многозначных алфавитов, используемых в логическом моделировании и генерации тестов, лежит классический двоичный алфавит  $\{0,1\}$ , образующий вместе с базисными логическими функциями булеву алгебру  $B_2$ . Существует два способа получения новой многозначной логики путем расширения некоторой исходной логики (A,F) (где  $A=\{a1,a2,...,ak\}$  – произвольный k-значный алфавит, F=(f1,f2,...,fm) – множество k-значных функций п переменных) до более мощной по значности логики  $(\widetilde{A},\widetilde{F})$ . При первом способе новый алфавит  $\widetilde{A}$  получается как подмножество некоторого декартового произведения исходного алфавита  $A:\widetilde{A}\subseteq A\times A\times...\times A$ . Второй способ заключается в том, что новый алфавит  $\widetilde{A}$  является некоторым множеством подмножеств элементов исходного алфавита:  $\widetilde{A}\subseteq 2^A$ . Произвольный элемент  $\widetilde{a}_i$  алфавита  $\widetilde{A}$  образуется как неупорядоченное подмножество элементов алфавита  $A:\widetilde{a}_i=a_{i1}\cup a_{i2}\cup...\cup a_{il}$ , где  $a_{ij}\in A$  [4].

**Тестирование.** В контексте тестирования неисправностей задержек путей, нам потребуется 5 значений: для констант 0 и 1, для переходов из 0 в 1 и из 1 в 0, а также неопределённое значение. Для этого есть рекомендация использования подмножества  $D_5$  16-значного алфавита  $B_{16}$  [5]. В данном подмножестве будут использоваться значения  $0=\{00\}$  — сохранение значений входов 0,  $1=\{11\}$  — сохранение значений входов 1,  $F0=\{00\cup 10\}$  — смена значений входов из 1 в 0, т. е. задний фронт,  $F1\{11\cup 01\}$  — смена значений входов из 0 в 1, т. е. передний фронт и  $u=\{00\cup 01\cup 10\cup 11\}$  — неопределённое значение. При анализе задержек

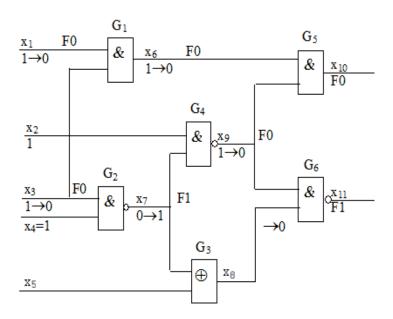

распространения сигналов на паре  $\langle X_1, X_2 \rangle$  переменных внешних входов, изменяющихся  $0 \rightarrow 1$  (передний фронт) присвоим значение F1. Аналогично переменным, с изменением  $1 \rightarrow 0$  (задний фронт) припишем F0. Переменные входов, сохраняющие значения на этой паре наборов, получают значения 0 и 1 соответственно. Далее тестируем схему с этими значениями. Результат моделирования в алфавите  $D_5$  приведен на рис. 1. Очевидно, линии схемы, получившие значения F0 и F1, являются кандидатами на включение их в пути, проверяемые данной парой наборов на неисправности типа задержка сигнала. Чтобы точно определить проверяемые пути, необходимо найти пути в схеме, начинающиеся на внешних входах и заканчивающиеся на внешних выходах, все линии которых имеют значения F0 или F1 и удовлетворяющие указанным выше условиям.

Рис. 1. Схема тестируемая алфавитом D<sub>5</sub>

Для приведённой выше схемы, устойчивым тестом является набор  $\langle X_1, X_2 \rangle = 11110,\,01010$  для пути  $P_1$  ( $x_3, x_7, x_9, x_{10}$ ), т. к. пути  $P_2$  ( $x_1, x_6, x_{10}$ ) и  $P_3$  ( $x_3, x_6, x_{10}$ ) не влияют на тест для  $P_1$ . Этот же набор является неустойчивым для P4 ( $x_3, x_7, x_9, x_{11}$ ) т. к. требуется установление значение сигнала на  $x_8$  в 1 до прибытия на G6 сигнала рассматриваемого пути P4.

Заключение. Таким образом, тестирование задержек на путях с помощью многозначного алфавита является эффективным т. к. из-за свойств многозначной логики, сразу учитываются сигналы до и после установления в схеме и получаются тесты проверяющие данные неисправности. Следует провести анализ эффективности данного метода на более сложных схемах и возможно выявить условия успешного получения теста для задержек на путях в зависимости от входов элементов.

## Список литературы

- 1. Матросова А.Ю. Классификация задержек путей // ТГУ 2009.

- 2. Скобцов Ю.А., Скобцов В.Ю., Нассер К.М. Построение тестов для перекрёстных неисправностей типа задержка // ДонНТУ -2011, № 14.

- 3. Patel J.H. A tutorial on delay fault testing // Department of Electrical and Computer Engineering University of Illinois. 2005.

- 4. Селиванов П.Е., Безрукова Л.М. Тестирование схем с помощью многозначных алфавитов //  $HИT\Pi Y. 2013$ .

- 5. Скобцов Ю.А., Скобцов В.Ю. Логическое моделирование и тестировании цифровых устройств. Донецк:ИПММ НАНУ, ДонНТУ, 2005.