### СПИСОК ЛИТЕРАТУРЫ

- Зыков А.А. Основы теории графов. М.: Вузовская книга, 2004. – 644 с.

- 2. Питерсон Дж. Теория сетей Петри и моделирование систем. Пер. с англ. М.: Мир, 1984. 264 с.

- Погребной В.К. Визуальный уровень представления алгоритмов функционирования распределённой системы реального времени на языке структурного моделирования // Известия Томского политехнического университета. – 2009. – Т. 314. – № 5. – С. 140–146.

- Погребной В.К. Матричный алгоритм решения задачи разрезания графов // Известия Томского политехнического университета. – 2007. – Т. 310. – № 5. – С. 91–96.

- Галкина В.Н. Дискретная математика: комбинаторная оптимизация на графах. – М.: Гелиос АРВ, 2003. – 232 с.

- Погребной Ан.В., Погребной Д.В. Исследование матричного алгоритма решения задачи разрезания графов // Молодёжь и современные информационные технологии: Труды VIII Всерос. научно-практ. конф. молодых ученых. – Томск, 2010. – С. 140–141.

Поступила 27.02.2012 г.

УДК 519.673

# АДРЕСУЕМАЯ ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ

А.А. Хамухин

Томский политехнический университет E-mail: aaxtpu@tpu.ru

Предложена функциональная схема адресуемой ячейки однородной вычислительной структуры для решения дифференциальных уравнений в частных производных. Показана возможность ускорения решения за счет снижения длительности цикла загрузки данных в регистры ячеек. Представлены сравнительные результаты моделирования линейки адресуемых и не адресуемых ячеек на примере решения тестовой краевой задачи с постоянными и переменными коэффициентами.

### Ключевые слова:

Адресуемая ячейка, однородная вычислительная структура, параллельные вычисления, дифференциальные уравнения в частных производных, постоянные и переменные коэффициенты.

### Kev words:

Addressable cell, homogeneous computing structure, parallel computation, partial differential equations, independent and dependent coefficients.

### Введение

В статьях [1—3] описаны примеры реализации вычислительных устройств для решения дифференциальных уравнений в частных производных на основе одинаковых ячеек однородной вычислительной структуры (ОВС), показаны возможности реконфигурирования ОВС в соответствии с заданными граничными условиями без аппаратных добавлений в схему ячейки, приведены дополнения, необходимые для решения задач с переменными коэффициентами. Основу такой ячейки составляют сумматоры и масштабные умножители, а информация о коэффициентах дифференциальных уравнений хранится в нескольких регистрах каждой ячейки. Разработан ряд схем реализации таких ячеек, на которые получены патенты [4—6].

Главным преимуществом однородной вычислительной структуры является синхронное аппаратное распараллеливание решения дифференциального уравнения, которое позволяет добиться наибольшей производительности на данном классе задач при прочих равных условиях по сравнению с другими типами вычислительных устройств. Вторым немаловажным преимуществом ОВС являются относительно низкие аппаратные затраты в пе-

ресчете на одну операцию по сравнению с универсальным многоядерным микропроцессором, в котором большая часть транзисторов просто простаивает при решении данного класса задач.

В этих статьях также сделано предположение, что реализация ОВС возможна на современных микросхемах типа БМК (известных за рубежом под аббревиатурой ASIC) или ПЛИС (известных за рубежом под аббревиатурой FPGA).

Наиболее известные реализованные проекты в этой области — это платформа RC100 фирмы SGI и суперкомпьютер фирмы Cray. Платформа RC100 содержит 35 модулей, каждый из которых имеет по две ПЛИС  $Altera\ Stratix\ III\ и\ 10\ блоков\ ло-кальной памяти. По данным фирмы <math>SGI$  платформа решает задачи биоинформатики в 900 раз быстрее, чем кластер из 68 узлов на базе универсальных микропроцессоров  $AMD\ Opteron\ [7]$ .

Суперкомпьютер *Cray XT5h* объединяет в единую систему скалярные процессоры (на основе *AMD Opteron*) и векторные процессоры на основе ПЛИС. Он компонуется из серверов двух типов: *Cray X2* и *Cray XR1*. Последний состоит из двух узлов, в каждый из которых входит микропроцессор *AMD Opteron*, связанный с помощью высокоско-

ростной шины *Hyper Transport* с двумя ПЛИС *Xilinx Virtex*-4. Масштабируемость системы позволяет объединять до 30 тыс. ПЛИС-процессоров в одной системе [8].

В России также ряд научных коллективов выполняет подобные разработки. Так, например, в НИИ многопроцессорных вычислительных систем Южного федерального университета (НИИ МВС ЮФУ, г. Таганрог) выполняется проект по созданию модульно-наращиваемой вычислительной системы с производительностью 20 Тфлопс, содержащей 1536 ПЛИС Virtex-5 в 19-дюймовой стойке [7]. Основу системы составляют базовые 16V5-1250P с производительностью модули 250 Гфлопс каждый, содержащие 16 ПЛИС Virtex-5 и соединяемые между собой в единый вычислительный ресурс с помощью скоростных *LVDS*-каналов. Четыре базовых модуля 16V5-1250P объединяются в конструктиве 1U вычислительного блока «Орион».

Хотя подобные вычислительные блоки, состоящие из реконфигурируемых полей ПЛИС, предназначены для решения более широкого спектра задач, чем решение дифференциальных уравнений в частных производных, их архитектура практически совпадает с архитектурой ОВС. Поэтому необходимо учитывать проблемы, возникающие с увеличением количества параллельно работающих блоков такой архитектуры.

В работе [9], представленной также НИИ МВС ЮФУ, эта проблема сформулирована как «кризис архитектуры реконфигурируемых вычислительных систем (РВС) на базе ортогональной коммутации». В работе отмечается, что с ростом степени интеграции ПЛИС растет потребность в увеличении количества каналов распределенной памяти. Однако конструктивные особенности базовых модулей не позволяют разместить достаточное количество каналов, поэтому реально наблюдается даже снижение производительности при увеличении количества вычислительных модулей при неизменном количестве каналов [9].

### Объект и цель исследования

Принципиальное отличие предлагаемых ячеек однородной вычислительной структуры от рассмотренных выше вычислительных блоков обусловлено ограниченным классом задач — решением дифференциальных уравнений в частных производных. Относительно небольшое количество коэффициентов дифференциальных уравнений и особенность матрицы, получаемой при аппроксимации дифференциального уравнения, позволяют использовать для хранения коэффициентов внутренние быстрые регистры. Это избавляет от необходимости обращения к относительно медленным внешним блокам памяти и ускоряет весь процесс решения.

Но при этом необходимо выполнить запись данных в регистры ячеек OBC перед началом цикла решения и считывание результатов из всех яче-

ек ОВС после окончания цикла решения. Поэтому при существенном увеличении количества ячеек в структуре можно ожидать эффект снижения общей производительности из-за влияния длительности загрузки данных в регистры ячеек. При частом повторении этой процедуры загрузки реальная производительность ОВС может существенно снизиться.

Объектом исследования является процесс загрузки данных в регистры однородной вычислительной структуры перед началом каждого цикла решения заданного дифференциального уравнения в частных производных.

Целью исследования является модификация схемы ячейки таким образом, чтобы снизить негативный эффект влияния длительности загрузки данных в регистры ячеек на общее время решения задачи.

### Модификация схемы ячейки

Традиционно все внутренние регистры ячеек ОВС для хранения начальной и текущей информации выполняются в виде сдвиговых регистров параллельно-последовательного действия. Параллельные выходы регистров используются масштабными умножителями в цикле решения задачи. Через последовательные входы и выходы все регистры соединены в цепь, первый вход и последний выход которой соединены с выводами ПЛИС. Через эти выводы и каналы связи внешнее устройство управления записывает коэффициенты дифференциального уравнения и считывает результат его решения [2]. Это известное применение сдвиговых регистров для преобразования последовательного кода в параллельный код и наоборот широко используется при передаче информации на большие расстояния, при записи информации на внешние носители, при работе с мониторами, видеокамерами и пр.

В одной микросхеме ПЛИС можно разместить несколько ячеек ОВС. Но для решения реальных задач требуются структуры с десятками тысяч таких ячеек. Поэтому необходимо комплексирование таких микросхем на платах, в блоках, в стойках. Количество выводов каждой микросхемы ограничено. Поэтому, с одной стороны, упомянутое выше экономное аппаратное объединение регистров в цепь позволяет существенно уменьшить количество выводов микросхемы, занятых на подготовительных операциях. Это позволяет увеличить соответственно количество выводов микросхемы, предназначенных для обмена данными между ячейками в цикле решения задачи и уменьшить время его выполнения. Но, с другой стороны, при переходе от параллельного кода к последовательному коду увеличивается время передачи данных. При этом циклы обмена данными чередуются с циклами решения уравнения [3]. Поэтому требуется дополнительное исследование влияния времени загрузки на общее время решения задачи для разных схем реализации ячейки.

Сочетание параллельного и последовательного кода можно применить ко всей ОВС либо к ее части, используя те или иные схемы коммутации. Все варианты соединения также требуют дополнительного исследования их влияния на общее время решения задачи. Кроме того, в некоторых случаях (при слишком большой длине цепи регистров) возрастает вероятность ошибок загрузки данных, для ликвидации которых может потребоваться многократная перезагрузка данных в регистры ОВС. В случае однородной вычислительной структуры, состоящей из сотен тысяч ячеек, это приведет к заметному увеличению общего времени решения.

Для снижения влияния последнего фактора предлагается применить техническое решение, хо-

рошо себя зарекомендовавшее в течение последних десятков лет при передаче данных в локальных компьютерных сетях и известное под названием *Ethernet*.

Это решение было предложено Р. Меткалфом и Д. Боггсом в 1975 г. [10]. В данном случае предлагается использовать не сам протокол *Ethernet* в полном объеме, а только принцип разбиения всей передаваемой информации на пакеты с обязательным заголовком в каждом пакете. В заголовке должен быть (кроме прочего) адрес ячейки-получателя и контрольная сумма. Таким образом, можно почти полностью исключить ошибки передачи данных, связанных с неправильной адресацией или сбоем при передаче данных.

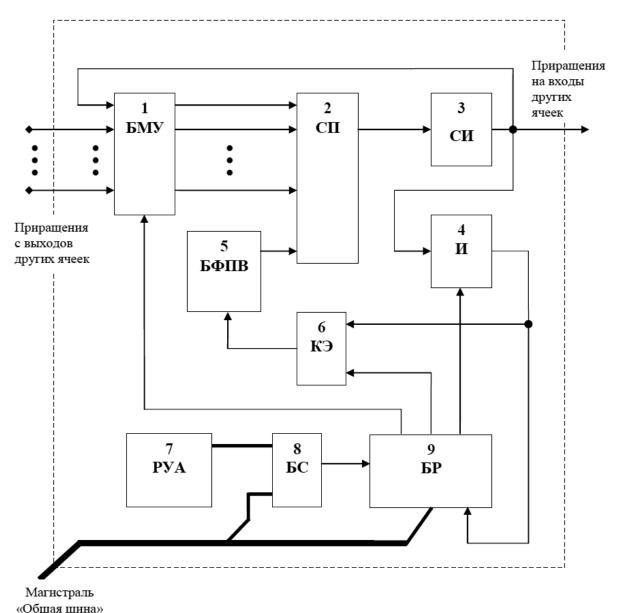

**Рисунок.** Функциональная схема адресуемой ячейки однородной структуры для решения дифференциальных уравнений в частных производных: 1) блок масштабных умножителей – БМУ; 2) сумматор приращений – СП; 3) следящий интегратор – СИ; 4) интегратор – И; 5) блок формирования приращений с предыдущих шагов по времени – БФПВ; 6) ключевые элементы – КЭ; 7) регистр уникального адреса – РУА; 8) блок совпадения – БС; 9) блок распределения – БР

Реализация этого принципа потребует модификации схемы ячейки, которую в отличие от известной схемы можно считать адресуемой ячейкой. Эта модификация связана с введением дополнительных аппаратных элементов в схему ячейки, что приводит к увеличению ее стоимости и размеров. Но это увеличение может быть оправдано при создании крупных однородных вычислительных структур, в которых время загрузки данных в регистры становится значительным и снижает реальную производительность всей ОВС. На схему адресуемой ячейки, представленной на рисунке, получен патент РФ [11].

Первые шесть элементов адресуемой ячейки полностью совпадают с известной схемой [3]. Новыми элементами ячейки являются: регистр уникального адреса РУА, блок совпадения БС и блок распределения БР.

Адресуемая ячейка, также как и не адресуемая, может находиться в двух состояниях, задаваемых внешним устройством управления. Первое состояние - это рабочий цикл вычислений (цикл решения уравнения), во время которого сигналы с выходов других ячеек (приращения) умножаются на коэффициенты в БМУ, суммируются в сумматоре СП, передаются в интегратор и при этом формируются выходные сигналы (приращения) для соседних ячеек. По сигналу окончания шага по времени от внешнего устройства управления ячейка переходит во второе состояние – цикл чтения/записи (цикл обмена данными). Во время этого цикла результат интегрирования передается в блок формирования приращений с предыдущих шагов по времени БФПВ и используется уже в следующем рабочем цикле вычислений ячейки, а также передается во внешнее устройство управления. Если необходимо (из постановки решаемой задачи), то во время этого цикла чтения/записи в БМУ записываются новые значения коэффициентов, полученные от внешнего устройства управления.

Все сдвиговые регистры, входящие в состав БМУ и других блоков, объединены в 1 или *п* цепей по последовательным входам-выходам. Это позволяет занимать под обмен данными с внешним устройством управления 2 или 2*n* выводов микросхемы. При сбое или сдвиге хотя бы на 1 бит последовательного кода все коэффициенты этой цепи будут неправильными, и возникнет ошибка в решении задачи, которую можно выявить только после следующего цикла обмена данными. Эту ошибку необходимо исправлять и загружать данные в регистры заново. Чтобы исключить эту потерю времени в каждую ячейку добавлен регистр уникального адреса РУА, который может быть закодирован при изготовлении микросхемы, и блок совпадения БС, который выявляет, совпадает ли значение, хранящееся в РУА, с адресом заголовка очередного пакета данных, поступающего в ячейку через магистраль «Общая шина». Если адреса совпадают, то блок БС дает разрешающий сигнал блоку распределения БР, который также подключен к магистрали. Блок БР распределяет данные, находящиеся в идентифицированном пакете данных по блокам ячейки: на ключевой элемент КЭ, в сдвиговые регистры блока масштабных умножителей БМУ и интегратора И. Временная диаграмма работы ячейки, описанная в работе [3], при этом не изменяется.

Снижение времени загрузки данных в ячейку достигается за счет того, что из магистрали «Общая шина» данные в параллельном коде поступают в блок распределения БР, который затем передает их в последовательном коде в цепь (цепи) сдвиговых регистров ячейки. Во время последней передачи данных внутри ячейки магистраль начинает обслуживать уже следующие ячейки.

Также обеспечивается и снижение потерь времени из-за необходимости повторять циклы чтения/записи в результате ошибок, связанных с отсутствием адресации при передаче данных от внешнего устройства в ячейки однородной вычислительной структуры.

### Исследование влияния длительности загрузки на общее время решение задачи

При решении краевых задач с постоянными коэффициентами загрузка данных в ячейку производится один раз в начале решения и общее время загрузки не зависит от количества итераций. Для задач с переменными коэффициентами загрузку новых коэффициентов необходимо делать после каждой итерации (группы итераций). В этом случае снижение времени загрузки данных в ячейку особенно важно. Модификация схемы ячейки, описанная выше, позволяет уменьшить длительность цикла обмена данными за счет того, что коэффициенты в каждую ячейку передаются по магистрали «Общая шина» параллельно. Для получения количественной оценки влияния цикла загрузки данных на общее время решения задачи применялось математическое моделирование решения краевых залач на ОВС.

Исследования проводились на математических моделях, представленных в работах [1–3]. Результаты моделирования в работе [1] приведены в виде таблицы, в которой показано количество итераций, полученных при решении задачи на модели ОВС, состоящей из 9 внутренних и двух граничных ячеек, при различной разрядности ячеек. При расчете общего времени решения на ОВС считалось, что на каждый такт цикла вычислений приходится один такт цикла обмена данными с внешним устройством, как это принято для не адресуемых ячеек.

Для сравнения времени решения задач на адресуемых и не адресуемых ячейках эта таблица была дополнена новыми результатами моделирования. При моделировании использовались уравнения, полностью идентичные описанным в работе [1] (задача с постоянными коэффициентами) и описанным в работе [3] (задача с переменными коэффициентами) при прочих равных условиях, указанных

в работе [1]. В таблице приведены результаты моделирования решения тестовой краевой задачи на однородной вычислительной структуре, состоящей из двух граничных ячеек и 9 внутренних (адресуемых и не адресуемых), при различной разрядности ячеек.

**Таблица.** Сравнение времени решения тестовой краевой задачи с постоянными и переменными коэффициентами на модели однородной вычислительной структуры

| Разряд-<br>ность       | Число так-<br>тов в одной | Количе-<br>ство ите- | Время решения задачи<br>с постоянными/переменными<br>коэффициентами, мс |                      |

|------------------------|---------------------------|----------------------|-------------------------------------------------------------------------|----------------------|

| ячейки                 | итерации                  | раций                | Не адресуемые                                                           |                      |

| , icinar               | терации                   | рации                | ячейки                                                                  | Адресуемые<br>ячейки |

| Заданная точность 0,01 |                           |                      |                                                                         |                      |

| 8                      | 28                        | *                    | _                                                                       | _                    |

|                        |                           | ·                    | _                                                                       |                      |

| 10                     | 210                       | *                    | -                                                                       | -                    |

| 12                     | 212                       | 148                  | 0,61/18,37                                                              | 0,31/15,11           |

| 14                     | 214                       | 112                  | 1,84/17,52                                                              | 0,93/12,13           |

| 16                     | 216                       | 108                  | 7,08/24,36                                                              | 3,55/14,35           |

| 18                     | 218                       | 106                  | 27,79/46,87                                                             | 13,90/24,50          |

| 20                     | 220                       | 106                  | 111,15/132,35                                                           | 55,58/66,18          |

| Заданная точность 0,1  |                           |                      |                                                                         |                      |

| 8                      | 28                        | *                    | _                                                                       | -                    |

| 10                     | 210                       | 70                   | 0,07/7,07                                                               | 0,05/7,05            |

| 12                     | 212                       | 57                   | 0,23/6,07                                                               | 0,13/5,83            |

| 14                     | 214                       | 56                   | 0,92/8,76                                                               | 0,47/6,07            |

| 16                     | 216                       | 60                   | 3,93/13,53                                                              | 1,98/7,98            |

| 18                     | 218                       | 60                   | 15,73/26,53                                                             | 7,87/13,87           |

| 20                     | 220                       | 60                   | 62,91/74,91                                                             | 31,47/37,47          |

<sup>\*</sup>Заданная точность решения недостижима.

Как видно из таблицы, при увеличении разрядности ячейки количество итераций решения краевой задачи стабилизируется. Время решения задачи с постоянными коэффициентами на адресуемых и не адресуемых ячейках растет пропорционально разрядности ячейки. Время решения задачи с переменными коэффициентами при небольшой разрядности ячеек существенно возрастает по

### СПИСОК ЛИТЕРАТУРЫ

- Хамухин А.А. Ячеечная модель устройства для решения дифференциальных уравнений в частных производных // Известия Томского политехнического университета. 2010. Т. 316. № 5. С. 62—67.

- Хамухин А.А. Реконфигурирование однородной вычислительной структуры с непрограммируемыми ячейками для решения дифференциальных уравнений в частных производных // Известия Томского политехнического университета. 2010. Т. 316. № 5. С. 68–72.

- Хамухин А.А. Модификация ячейки однородной структуры для решения дифференциальных уравнений в частных производных с переменными коэффициентами // Известия Томского политехнического университета. – 2011. – Т. 318. – № 5. – С. 37–41.

- Ячейка однородной структуры для решения дифференциальных уравнений в частных производных: пат. 2359322 Рос. Федерация. № 2007141832/09; заявл. 12.11.07; опубл. 20.06.09, Бюл. № 17. 6 с.

сравнению со временем решения задачи с постоянными коэффициентами, но при увеличении разрядности они становятся сопоставимыми. Это можно объяснить тем, что при увеличении разрядности ячеек длительность цикла вычислений существенно увеличивается, а длительность цикла обмена данными с ячейкой остается прежней.

Во всех сопоставимых примерах расчетов, приведенных в таблице, модель OBC на адресуемых ячейках показала меньшее время решения задачи, чем модель однородной вычислительной структуры на не адресуемых ячейках.

Есть основания предположить, что при увеличении количества ячеек в OBC влияние длительности загрузки на общее время решения задачи будет снижаться, поскольку длительность цикла вычисления увеличивается более значительно, чем длительность цикла обмена данными.

### Выводы

- Предложена модифицированная функциональная схема адресуемой ячейки однородной вычислительной структуры для решения дифференциальных уравнений в частных производных.

- 2. Модификация заключается в том, что данные из магистрали «Общая шина» в ячейку поступают в параллельном коде и при их распределении по сдвиговым регистрам внутри ячейки магистраль освобождается для обслуживания других ячеек.

- 3. Применение схемы адресуемой ячейки ускоряет решение дифференциальных уравнений в частных производных за счет снижения длительности цикла загрузки данных, особенно в задачах с переменными коэффициентами.

- 4. Результаты моделирования на примере решения тестовой краевой задачи подтвердили работоспособность и эффективность модифицированной ячейки.

Представленная работа выполнена в рамках государственного задания «Наука».

- Ячейка однородной структуры для решения дифференциальных уравнений в частных производных с переменными коэффициентами: пат. 2419141 Рос. Федерация. № 2009128437/08; заявл. 22.07.09; опубл. 27.01.11, Бюл. № 14. 7 с.

- Устройство для вычисления дискретизированного непрерывного вейвлет-преобразования: пат. 2437147 Рос. Федерация. № 2010127068/08; заявл. 01.07.2010; опубл. 20.12.2011, Бюл. № 35 9 с.

- Каляев И.А., Левин И.И. Реконфигурируемые мультиконвейерные вычислительные системы для решения потоковых задач обработки информации и управления // Параллельные вычисления и задачи управления (PACO'2010): Матер. V Междунар. конф. – М., 26–28 октября 2010. – М., 2010. – С. 5–19.

- Суперкомпьютер Cray XT5h // Лаборатория Параллельных информационных технологий НИВЦ МГУ. 2009. URL: http://parallel.ru/computers/reviews/CrayXT5h.html (дата обращения: 26.04.2011).

- Левин И.И. Реконфигурируемые вычислительные системы с открытой масштабируемой архитектурой // Параллельные

- вычисления и задачи управления (PACO'2010): Матер. V Междунар. конф. M., 26–28 октября 2010. M., 2010. C. 83–95.

- Metcalfe R.M., Boggs D.R. Ethernet: Distributed Packet Switching for Local Computer Networks. 1975. URL: http://ethernethistory.typepad.com/papers/EthernetPaper.pdf (дата обращения: 11.01.2011).

- Адресуемая ячейка однородной структуры для решения дифференциальных уравнений в частных производных: пат. 2427033 Рос. Федерация. № 2010107933/08; заявл. 03.03.10; опубл. 20.08.11, Бюл. № 23. 7 с.

Поступила 02.05.2012 г.

УДК 004.42

## АРХИТЕКТУРА РАСПРЕДЕЛЕННОГО ВЫЧИСЛИТЕЛЬНОГО КОМПЛЕКСА ДЛЯ ДВУМЕРНОГО АНАЛИЗА ИЗОБРАЖЕНИЙ ДИСКОВ ДЕРЕВЬЕВ

И.А. Ботыгин, В.Н. Попов, В.А. Тартаковский\*

Томский политехнический университет \*Институт мониторинга климатических и экологических систем CO PAH, г. Томск E-mail: botygin@ad.cctpu.edu.ru

Разработана архитектура и алгоритмы реализации распределенного вычислительный комплекса обработки дендроэкологических данных. Представлена GPSS-модель комплекса для оценки эффективности его функционирования. Практическая реализация комплекса осуществлялась с использованием стека свободно распространяемых программных продуктов. Проиллюстрирована работа комплекса на таких задачах двумерного анализа изображений дисков деревьев, как вычисление азимута и среднеквадратичной ширины области максимального прироста, а также вычисление значений индексов прироста ширины колец деревьев.

#### Ключевые слова:

Дендроэкология, дендрохронология, древесные спилы, годовые кольца деревьев, математическая модель, серверное приложение.

### Key words:

Dendroecology, dendrochronology, tree stem disk, tree-rings, mathematical model, server application.

## Программное обеспечение в области дендрохронологии

Проведенный обзор и сравнительный анализ существующих аппаратно-программных комплексов и систем для анализа и обработки данных в области дендрохронологии показал, что они являются ограниченными для использования и ориентированы на решение новых задач, связанных с неоднородностью окружающего пространства. Особенностью таких задач является большой объем данных, которые необходимо хранить, обрабатывать и сопоставлять между собой, пространственная распределенность мест сбора образцов.

В таких условиях оптимальным системным решением, обеспечивающим повышение вычислительной мощности, увеличение объема хранимых данных, является использование технологии распределенной их обработки. Эта технология подразумевает физическое распределение хранения и обработки данных в пространстве на нескольких вычислительных машинах, которые связаны между собой каналами передачи данных, координацию их вычислительных мощностей, использование стандартных протоколов и служб сетевого взаимодействия. В данное время существует множество инструментальных средств технологий распределенных вычислений, а также проектов, реализованных с их использованием, но для мониторинга

климатических и экологических изменений на основе биоиндикации такие технологии не применялись. Таким образом, реализация технологии распределенных вычислений и разработка алгоритмического обеспечения для дендрохронологических исследований, связанных с двумерным анализом изображений спилов деревьев, даст возможность получать новые результаты и качественные оценки параметров окружающей среды.

В настоящей работе описывается реализация технологии распределенных вычислений и разработка алгоритмического обеспечения для дендрохронологических исследований. Безусловно, дендрохронологические исследования - это только часть мониторинга, моделирования и прогнозирования климатических и экосистемных изменений под воздействием природных и антропогенных факторов. Но особенность задач дендроэкологического анализа, заключающаяся в необходимости математической обработки очень большого объема данных (временные ряды наблюдений могут достигать сотен гигабайт), широком спектре решаемых задач, коллективной работе многих сотрудников на всех этапах дендроэкологических исследований, а также в необходимости хранения и систематизации больших объемов неоднородной структурированной информации (собственно хронологические ряды наблюдений, результаты обработки,