# Design of a kilowatt DC-DC converter

Hongxing Liu<sup>1</sup>, Chenwei Fu<sup>1</sup>, Na Li<sup>1</sup>, Soldatov Alexey<sup>2</sup>, and Wei Han<sup>1,\*</sup>

**Abstract.** In view of the low power of traditional DC-DC converters, a DC-DC converter with a kilowatt power is designed. The input signal's frequency is 1 kHz and the duty cycle is 5%. The PWM signal controls the high-speed conduction or cut-off of the switch tube. The input DC voltage is 36V, and the output voltage is twice as high as the input voltage. The output power is greater than 1 KW; the circuit conversion efficiency is 87.21%.

### 1 Introduction

At present, DC-DC converter mainly works on a low-power voltage doubling, voltage inversion and other aspects. The mainstream applications are the battery-powered mobile phones, digital cameras and other fields to drive LED backlight which should be provided with appropriate power [1-3]. Another very extensive application is EEPROM and flash memory to provide read and write power, the memory of the power rail is generally 1.8 V, 3.3 V, as read needs +5 V and erase needs +12 V, that's why we integrate the DC-DC converter into the IC for single-supply operation [4-7].

For the current charge pump applications, the main problem is the difficulty to achieve high-power, high-voltage applications, as high-power aspects of inductive switching DC-DC converter occupies an absolute advantage [8-11]. But the charge pump has the advantages of small volume, high efficiency, low quiescent current and low minimum operating voltage, so it is more important to design and manufacture a high-power charge pump [12, 13]. In this paper, the circuit is designed and produced by MATLAB simulation software. The output power of the charge pump is more than 1 KW and the conversion efficiency is 87.21% by PWM signal controlling the switch while charging and discharging the capacitor.

## 2 DC-DC converter design

#### 2.1 DC-DC converter twice the boost principle

Commons Attribution License 4.0 (http://creativecommons.org/licenses/by/4.0/).

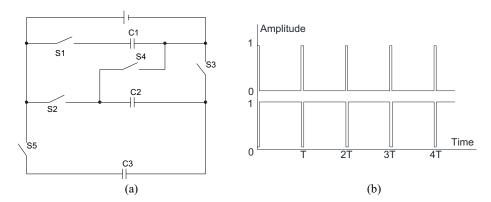

The principle of the DC-DC converter double boost shown in Figure 1(a), using capacitor charge and discharge to achieve an output voltage that is twice the input voltage. First,

© The Authors, published by EDP Sciences. This is an open access article distributed under the terms of the Creative

<sup>&</sup>lt;sup>1</sup>Jilin University, College of Physics, 1505 Linyuan Road, Changchun, China <sup>2</sup>Tomsk Polytechnic University, 634050 Tomsk, Russia

<sup>\*</sup>Corresponding author: whan@jlu.edu.cn

close the S1, S2, and S3 switches, and the capacitors C1 and C2 (called C1 and C2 for the pump capacitance) are charged in parallel. The DC power supply charges the capacitor almost instantaneously. Then, S1, S2 and S3 are turned on while the other set of switches S4 and S5 are closed, and C1 and C2 are in series to provide power for C3 (called the load capacitance).

Under ideal conditions, the two pump capacitors are connected in parallel to a power supply in order to charge until voltage is 36 V. The next stage is to connect the capacitors in series in order to charge it till 72 V, in order to achieve a double boost through doubling the input voltage.

## 2.2 Design of MATLAB simulation circuit

As shown in the following circuit diagram, MATLAB software has been used to design and simulate the circuit. The power supply is a DC power supply and is set to + 36 V. Switch can be used as a general-purpose switch, respectively, for each switch input phase reversed PWM control signal. A PWM control signal having a duty ratio of 5% is inputted for S1, S2 and S3, and a PWM control signal having a duty ratio of 95% is inputted to S4 and S5, with a delay of 0.000005 second from the previous signal, to realize controlling the two sets of switches at the same time. The control signal diagram is shown in Figure 1(b).

Fig. 1. (a) DC-DC converter twice the boost principle, (b) Input PWM control signal.

These two processes complete one charge and discharge process, the whole process is completed in a PWM cycle. The capacitor charging formula is as follows:

$$V_t = V_u \cdot \left[ 1 - \exp\left(-\frac{t}{RC}\right) \right] \tag{1}$$

Where,  $V_t$  means the voltage across the capacitor for time t,  $V_u$  means the voltage after the capacitor is fully charged, R is the load resistance value and C is the charging capacitance value, which is calculated by the formulas:

$$t = 2RC, V_t = 0.86V_u \tag{2}$$

$$t = 3RC, V_t = 0.95V_{tt} \tag{3}$$

$$t = 4RC, V_t = 0.98V_u \tag{4}$$

$$t = 5RC, V_t = 0.99V_{tt}, (5)$$

Visibly, after 5RC time of the charge, the capacitor is almost full charge. Discharge formula is as follows:

$$V_t = V_u \cdot \exp\left(-\frac{t}{RC}\right) \tag{6}$$

When the time *t* tends to infinity, the voltage is reduced to zero. The charge of the load capacitance is required to be charged more than the pump capacitance with respect to the charging process, so that a PWM control signal having a duty of 5% is inputted to *S1*, *S2* and *S3*, and a control inverting signal is inputted to *S4* and *S5*. As the capacitor charge and discharge processes are nonlinear, processes needs to be repeated in order to achieve the accumulation of charge, that is, to achieve the capacitor's charging.

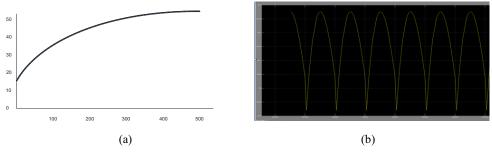

Fig. 2. (a) Output voltage waveform before filtering, (b) Filtered ripple waveform.

The capacitance of each pump capacitor is 250 V, 2200  $\mu F$  and 0.01  $\Omega$ , which is equivalent to 250 V, 550  $\mu F$  and 0.0025  $\Omega$ . The internal resistance of shunt capacitor is reduced, which can greatly reduce the loss of the circuit. Maxwell load capacitors were selected at 2.7 V, 350 F, 0.1  $\Omega$  super capacitor, the two capacitors in series, making it increase in the voltage across the capacitor.

In order to test the output power of the load capacitance, load resistance is added to the load capacitance's circuit. Testing the value of voltage and the current on the branch of the load resistance circuit can provide the output power of the load capacitance.

After the simulation test, it has been observed that the output voltage ripple is large and in order to obtain an ideal DC voltage, a filter is added to the load capacitance of the output voltage. The filter inductance value is selected at 3.3 mH. A very large inductor value will increase the circuit resistance, and thus increase losses. The ripple factor after filtering is 0.35 V, the ripple coefficient is reduced to 0.62%, and the ripple factor satisfying the circuit design requirement is less than 1%. Before and after the effect of filtering comparison chart is shown in Figure 2(a) and Figure 2(b).

## 3 Results and analysis

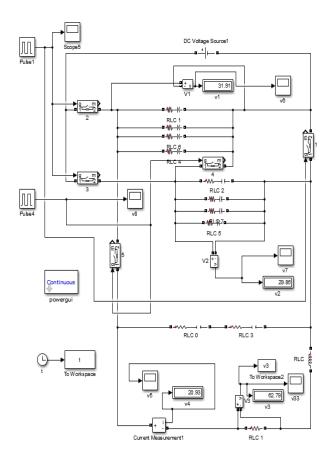

Figure 3 shows the simulation results where the input frequency is 1 kHz, duty cycle is 5% of the PWM signal. From the simulation results, it can be seen, that the final output voltage is 62.79 V and the output current value is 20.93 A. The output power is  $P = UI = 62.79 \cdot 20.93 = 1314.19$  W, to achieve the purpose of designing the circuit. The circuit is a two-fold boost circuit, the ideal output voltage of 72 V, because of the presence of internal resistance, there is a certain loss, so conversion efficiency  $\eta = 62.79 / 72 \cdot 100\% = 87.21\%$ , higher than the traditional charge pump conversion efficiency.

Fig. 3. MATLAB simulation results.

#### 4 Conclusions

In order to solve the problems of current charge pump, the simulation of the software is carried out by MATLAB. The output voltage of the charge pump circuit is twice as large as the input voltage and the output power of the circuit is more than 1 KW by selecting the components and designing the circuit. This paper is based on the advantages of DC-DC converter, the design of lower cost, higher output power, higher conversion efficiency of the charge pump, breaking the traditional charge pump low power limitations.

### References

- 1. Z Jinqing et al. Mod. Electr. Tech 37, 148 (2014)

- 2. J Kai, Z Ying, Microelectr J **45**, 599 (2015)

- 3. F. Canales et al., IEEE Trans. Power Elect. 17, 898 ( 2002)

- 4. E. Juarez-Hernandez, ICECS 1, 349 (2001)

- 5. J.A. SABATE et al., IEEE APEC, 275 (1990)

- 6. M.J. Schutten, IEEE Trans. Power Elect. 18, 659 (2003)

- 7. L. Mateu, F. Moll, SPIE **5837**, 359 (2005)

- 8. Chao Lu et al., DATE, 1602 (2010)

- 9. J. F. Dickson, IEEE J Solid-State Circuits 11, 374 (1976)

- 10. Jieh-Tsorng Wu, Kuen-Long Chang, IEEE J Solid-StateCircuits 33, 592 (1998)

- 11. Grigorev A.P. et al., *Mod Tech+Technol* **896064**, 97 (2000)

- 12. A.I. Soldatov et al., SIBCON, 7491869 (2016)

- 13. E.Y. Burkin, O.A. Kozhemyak, Instrum Exp Tech+ **59**, 245 (2016)